# Software Solutions for RF Module Development

Figure 1: Miniaturized consumer electronics will be among the devices requiring radio modules to provide wireless connectivity (Image courtesy of Striiv).

This white paper explores the fundamental design challenges faced when creating and producing high-frequency modules for a range of wireless system applications, and the tools required for an effective workflow supporting the design and integration of these modules in the shortest time possible.

Much of this capability can be addressed using the NI AWR Design Environment platform to define and manage the electrical and physical attributes of a wireless module and to perform circuit, system, and electromagnetic (EM) co-simulation within a single integrated environment that also supports interoperability with industry-leading CAD layout tools.

### Trends Driving Module Development

Developing the many wireless devices and supporting infrastructure that will connect future smart hardware such as internet of things (IoT), advanced driverassist systems (ADAS)-enabled vehicles, wearables (Figure 1), and biomedical devices will be a massive engineering effort requiring cost-effective RF front ends that can be manufactured for mid- to high-volume production. Much of this RF connectivity will be achieved through ICs combined into multi-functional modules containing all of the circuitry needed to transmit and receive RF signals.

As a self-contained subassembly, today's RF modules are drop-in components that provide wire-

less connectivity for all types of systems, including monitoring and remote-control equipment. These modules may include an integrated antenna or a connector for an external antenna, as well as a serial interface for communication to the host processor. They are typically shielded to limit unintended emissions and increase electromagnetic compatibility (EMC) immunity.

RF design is notoriously complex due to radio-circuit sensitivity and the accuracy needed to simulate components and associated layouts when targeting a desired performance at a specific frequency. In addition, reliable RF circuits require tight tolerances of the manufacturing process to ensure that the performance is not adversely affected. Radio circuits are usually subject to limits on radiated emissions, requiring conformance testing and certification by a standardization organization such as European Telecommunications Standards Institute (ETSI) or the U.S. Federal Communications Commission (FCC).

Consequently, engineers will often design a circuit that requires radio communication using a premade radio drop-in module rather than attempting their own discrete design. This approach often saves time and money on development. To serve this design trend, manufacturers of discrete RF components may need to consider adding modules

with integrated RF functionality into their own product portfolios.

# Integrating Functionality – Systems/Subsystems Approach

Creating new, multi-die heterogeneous modules and corresponding system boards involves multiple engineering teams with different perspectives. Module designers, organized into a multidisciplinary team, must cooperate to solve numerous optimization problems, including system input/output ( I/O) requirements, thermal and signal integrity constraints, die placement and orientation, stacking configurations, package substrate and interposer design, and interconnect design at the IC and package level, all while taking into account the constraints on the system's printed circuit board (PCB).

Although it is possible to organize the different design disciplines in a coordination meeting, a successful joint plan really requires a methodology, a process, and the design technology/automation for tying these worlds together. When integrating transmit/receive functionality into a single device, a system approach helps delegate individual radio-block development while managing the overall electrical, mechanical, and thermal design.

System simulation tools that operate in conjunction with phy-

RF modules offer a large amount of functionality in a small space, but they can be an engineering challenge for development teams. When combining multiple integrated circuits (ICs) into a single package, it is necessary to model the electrical behavior of many different technologies, such as interconnects (transmission lines) and embedded distributed components, as well as RF, analog, and digital components. The choice of computer-aided engineering (CAE) software can be critical for achieving simulation results that are closely matched to final measured results.

National Instruments ni.com/awr

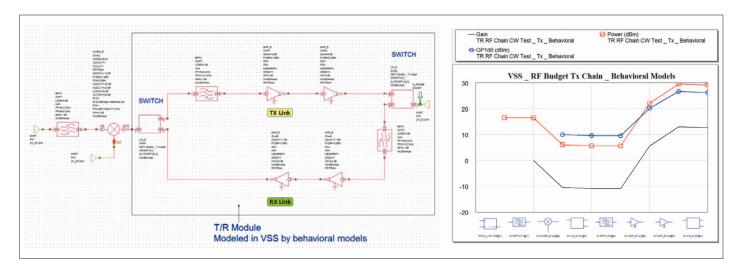

Figure 2: System-level budget analysis based on behavioral models provides support for system architecture development and component specification.

sical realization tools support top-down/bottom-up analysis that enables these different engineering teams to obtain design requirements from a single 'master' plan and compile individual results into an evolving simulation model of the entire module. The system architecture defines the arrangement of the individual radio blocks and their performance requirements. while system simulation based on behavioral models supports first-pass component specification from RF-budget measurements that include gain, power level, IP3, noise figure, and more, as shown in Figure 2.

VSS system simulation software provides designers with a comprehensive library of RF and digital signal processing (DSP) behavioral models to create and analyze end-to-end communication systems or module-based transmit/receive subsystems. Operating within the NI AWR Design Environment platform, VSS also supports co-simulation with detailed circuit- and EMbased designs from the Microwave Office circuit simulator, as well as the AXIEM 3D planar and Analyst<sup>TM</sup> 3D finite element method (FEM) EM simulators. This system/circuit/EM cosimulation capability provides the design verification necessary when integrating functionality into a small form factor.

### **Design Partitioning**

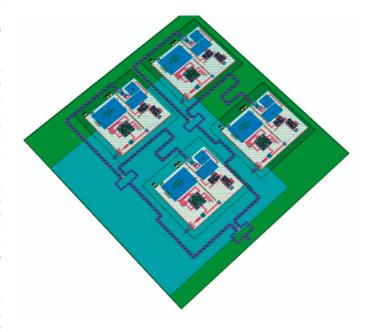

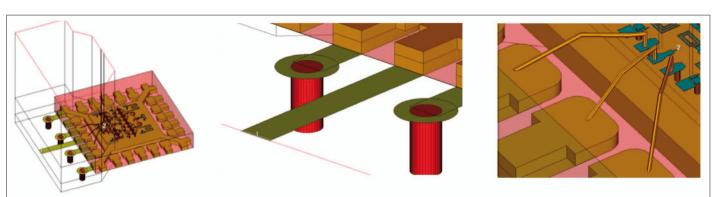

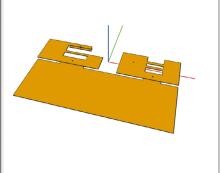

Early in the module design process, the exact capabilities of the module must be determined, including the overall footprint, location of I/O ports, available power supplies, and underlying architecture. Engineering teams can then focus on the physical, electrical, and thermal aspects of the module development, which include physical partitioning such as component placement, orientation, and shielding, as well as the electrical partitioning, which breaks down to power supply distribution, RF routing, placement of sensitive circuits and associated signal paths, and providing adequate grounding, as shown in Figure 3.

For RF designs, physical and electrical considerations are intertwined. For example, designers will try to separate highpower RF amplifiers (HPAs) from low-noise amplifiers (LNAs) as much as possible in order to reduce their interactions. Shielding and placement of components on opposite sides of the module substrate are among the techniques used to keep highpower RF transmitter circuits from interfering with low-power RF receiver circuits.

When possible, RF outputs generally need to be well separated from RF inputs and sensitive analog signals should be kept well away from high-speed digital and RF signals. In addition, a

module should have at least one ground plane that is as solid as possible, generally without partitions and with a minimum of voids (cutouts).

In addition to physical implementation, system verification is a critical part of module design. Accurately simulating high-frequency electronics requires system-level analysis that captures the behavior of diverse physical structures using a range of modeling technologies.

Simulation of a complete signal path (or channel) requires accurate circuit/netlist or system-

level behavioral modeling of ICs, all chip-to-chip interconnects (including IC packages, PCB traces, connectors, and vias with associated bypass capacitors), associated power-distribution structures (planes in the package and PCB, decoupling capacitors, and stitching vias), and embedded (off-chip) passive components.

### Integrating Heterogeneous Technologies

The integration of one or more ICs onto multi-level substrates

Figure 3: Module development must provide required functionality within a given form factor and I/O port alignment such as this feed network for a 2 x 2 phased-array patch antenna.

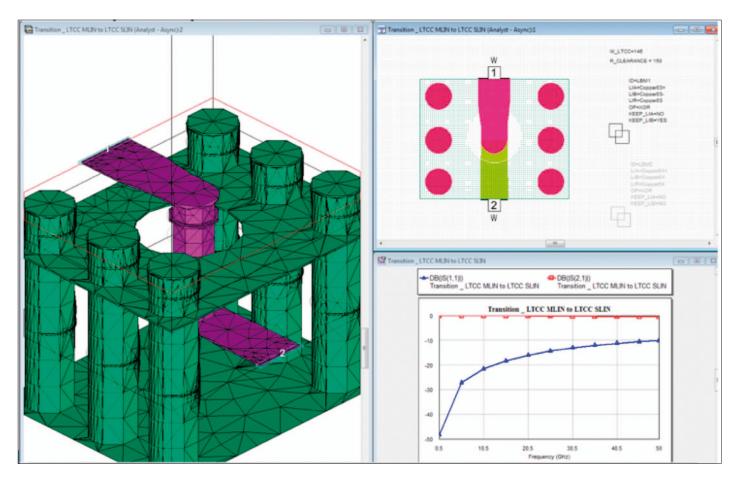

Figure 4: EM simulation is often required to electrically characterize passive components and interconnects such as transitions between layers of multi-layer substrates.

is a challenging task at higher frequencies where electrical characterization must be performed using EM simulation of structures implemented via layoutfocused design tools, as shown in Figure 4. In this design phase, the focus is on electrical modeling of the floor plan while addressing the physical I/O requirements of the IC, integrating the package substrate constraints and variables, and considering the multiple PCB platforms (form factors) with which the module is intended to work.

Given how frequently traces are rerouted to suit the repositioning of components within a module during the design phase, circuit/ EM co-simulation allows the electrical impact of trace rerouting to be addressed in real time. To support the physical design, many layout tools offer powerful place-and-route automation, which helps designers efficiently place electronic components within a limited amount of

space. This is followed by routing, which determines the optimum wiring path based on a set of defined rules and limitations of the manufacturing process. Since the width and length of these traces will influence the electrical performance for RF designs, their influence needs to be accounted for in simulation, but not necessarily in a schematic, where a shorted wire between element nodes may be preferable.

The iNet™ intelligent net technology within NI AWR software enables designer, for instance, to draw a simple short-circuit interconnect in the electrical schematic diagram and then in the layout route that interconnect with the internal knowledge of the technology being used. With iNets, designers can have a wire on the schematic that is routable over many layers, with an auto via insertion capability that knows how to terminate the route on whatever pin(s) to which it is

connected. iNet technology lets users route a wire in their schematic, which ultimately enables them to incrementally model it as they refined their design along the way to tapeout. This enables them to address interconnects right up front in the schematic and dynamically synchronize them with the rest of the flow, from layout to EM simulation and verification.

Advanced packaging research and development teams must work closely with system and circuit design teams to optimize interconnect and embedded passive technologies for size, reliability, and performance, and to develop and incorporate parametric-based RF models within existing design flows. Considerable research activity is dedicated to characterizing and modeling the RF properties of various assembly techniques in order to reduce parasitics and optimize the signal transmission characteristics. Special interest focuses on different bonding techniques such as wire bonding, flip chip, ribbon bonding, embedded chip solutions, and more, as well as on-passive components such as resistors, capacitors, inductors, transformers, and transmission lines. Substrate technologies such as low-temperature co-fired ceramic (LTCC) and multi-layer organics are among the more popular materials being developed for RF applications.

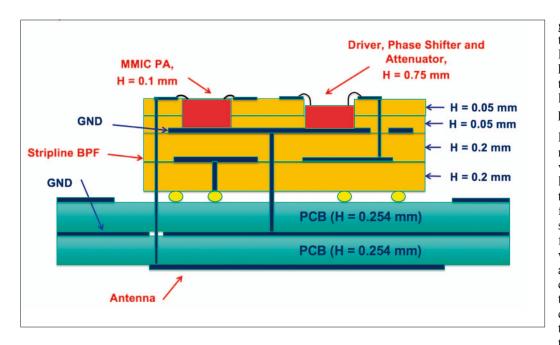

Depending on the intended functionality of the module, integration may require a set of technologies such as wafer thinning, embedded passive components, vertical system integration, assembly of thin components, thin interconnect technologies, bumping/ball placing, and dicing. All these technologies need to be optimized and adapted in a modular integrated process flow. Advanced module packaging acts as a system-integration carrier, with the potential to reduce the

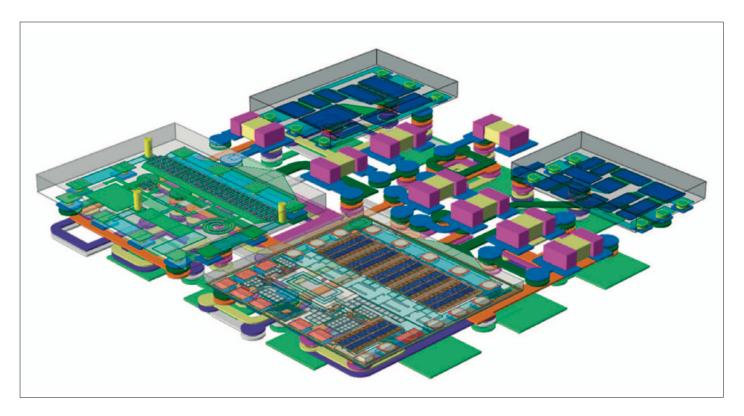

Figure 5: Modules rely on advanced interconnect technology, multi-layer substrates, and component stacking to reduce the device footprint while increasing overall functionality.

packaging cost and increase the functionality of a system at the same time (Figure 5).

## Interconnect Technology – EM Simulation and Modeling

Optimizing the performance of the transition between different substrates is a common design requirement for module designs with different IC and PCB process technologies. For example, a designer might be interested in the transition between a board and a ball-grid arrayed module, or between a quad-flat no-leads (QFN) package and a chip, by using bond wires (Figure 6). To address this problem, an engi-

neer may create a single model using EM analysis to extract the S-parameters for the combined structure representing the I/O port of the board, the transition itself, and the I/O port associated with the QFN package. The board and package ports (wirebond pads) would be based on their respective substrate stackup (layers, materials, and more). The S-parameter response could then be inserted into the schematic for subsequent circuit simulations.

A superior design flow manages multiple, heterogeneous technologies within a single hierarchical project. At the circuit simulation and layout level, each module component can be defined by a schematic containing an arrangement of elements from a process design kit (PDK) that includes the electrical characteristics of the element for a range of operating conditions such as frequency and input power, and details of the substrate stackup. Figure 6 shows such a design flow.

The stack-up data provides information for the processing masks used later in manufacturing and dictates the model behavior of distributed components such as transmission lines and discontinuities such as microstrip-width steps, tee-sections, and bends. By using multiple libraries/PDKs for different manufacturing technologies, designers can easily inte-

grate board, module, and chip technologies within the same EM project. This is accomplished in NI AWR software with the concept of hierarchy in the layout and automation developed in the EM interface.

For instance, the top schematic may represent the board with the various models, design rules, and layout settings, all specific for that board. Layout cells come from the board PDK. Another schematic could be developed for the chip design, using a PDK with the corresponding models and layout cells. With hierarchy, the schematic describing the chip can be used as a subcircuit to the board schematic in the module design. In this way, the designer can simulate both the board and chip together as a single network. For the wirebonded chip-to-board example, the structure represents an interconnect that requires 3D EM simulation, since the wire bond is a 3D object and the bonding pad of the IC is adjacent to the edge of the die (planar EM solvers assume infinite dielectric layers in their formulations). Three-dimensional shapes are handled by extrusion of the polygons or by using 3D cells. Extrusion is a straightforward method in which a 2D polygon is drawn and a vertical distance is specified, either upward or downward.

In this chip-package-board design flow, the EM SocketTM architecture within NI AWR software streamlines the sharing of model layout informa

Figure 6: a) A monolithic microwave IC (MMIC) in a QFN package on a Duroid board. The launch has been drawn at Port 1, which goes onto the flat package and then to the MMIC via bond wires at Port 2. b) Grounding vias from the board PDK. c) A closeup of the bond wires.

Figure 7: RF module design flows support laminate (PCB) design and integration of MMICs, RFICs, BAW/SAW filters, and other surface-mount technology (SMT) components.

tion between NI AWR tools and third-party EM simulators. The layout is automatically "flattened" before being sent to the EM simulator, meaning the hierarchy of the layout is removed and the layout consists of the various dielectric layers and shapes of all the subcells merged into one layout. The design can therefore solve multi-technology layouts in place using the Analyst simulator or through the EM Socket technology to other 3D simulators such as ANSYS HFSS or D'Assault Simula (formerly CST), without worrying about hierarchy and how layout cells are handled.

From the described module design flow, Microwave Office software enables users to quickly take advantage of features such as:

- multiple PDKs and libraries for different physical technologies

- ability to drive multiple simulators from one set of layout rules, layer stackup definitions, and shape simplification rules

- use of 3D cells in a 2D layout to support both layouts in one environment

- control of EM simulation results from different simulators using data sets

#### **RFIC Integration**

A module can be designed with off-the-shelf or custom RFICs/ MMICs. Off-the-shelf components are often designed to a characteristic impedance of 50 ohms and come with electrical operating and die attach instructions in the form of a datasheet or application note. For this scenario, the amount of RF design required to integrate the IC with the module may be minimal, perhaps nothing more than addressing the impact of the interconnecting wire-bond inductances. For custom RFICs or other components such as bulk acoustic wave (BAW) and surface acoustic wave (SAW) filters, off-chip elements may be required, and the RFIC component design and integration efforts may be shared by the RFIC and module laminate designers, as shown in Figure 7.

A large percentage of RFIC intellectual property (IP) has been and continues to be developed in Cadence Virtuoso software. Consequently, a comprehensive module design flow must provide RFIC designers with laminate (electrical design) details and laminate (PCB) designers with the electrical details (S-parameters, simulation-ready netlist or behavioral models) of the RFIC. Therefore, the design tool should accommodate the designers' need depending on the focus of the individual design task or particular integration challenge of the module project. Interoperability between tools is necessary to the extent that design information needs to be shared between designers.

Recently Cadence Design Systems and NI announced a broad-ranging collaboration to improve the overall semiconductor development, design, and test process of "next-generation wireless, automotive, and mobile ICs and modules." At the same time, Cadence launched a new Virtuoso RF solution, supporting the design of RF modules and RFICs with passive-device modeling made possible through the integration of NI AWR software, specifically AXIEM 3D planar Em simulator, within the Virtuoso custom IC design platform.

This approach provides seamless integration between the IC and package substrate design teams supporting the design of modules featuring off-chip devices and multiple ICs based on differing PDKs. Module complexity drives the need to integrate more powerful layout/circuit management, simulation tools for ultra-large networks, and EM simulation with the ability to incorporate the impact of physical design on electrical performance into a highly-automated design flow that reduces potential design failures.

Module designs have many moving parts and the RF sections require support from specialized automated simulation technologies such as load-pull analysis, harmonic-balance simulation, and circuit envelope for nonlinear devices, as well as design aids that accelerate the initial

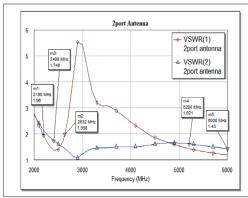

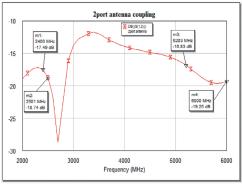

Figure 8: Antenna design for an IoT module with embedded dual-band WiFi connectivity.

stages of circuit development and physical realization.

#### Synthesis and Embedded Antennas

Modules targeting 5G and IoT devices may need to offer embedded antenna solutions optimized for performance, cost, and size. Furthermore, multiple-inmultiple-out (MIMO) technology using multiple antennas on a single device will provide greater throughput and performance reliability. This requires not only good antennas, but also high isolation between them, which can be achieved by physically separating the antennas, but may not be possible with an integrated module. High isolation can also be achieved between closely-spaced internal antennas by using chokes, matching networks, and other techniques, each having their own advantages and drawbacks.

The AntSynTM antenna synthesis module enables designers to synthesize compact MIMO antennas automatically from user requirements, enabling them to meet size, cost, and performance requirements. AntSyn software combines advanced optimization algorithms, expert systems, and EM simulation to convert user input regarding the antenna's electrical and physical requirements into a physical design.

For example, AntSyn software was used to create both the two-port and three-port MIMO antennas shown in Figure 8. This compact device addresses the following design goals:

- dual-band WiFi operating at 2.4 and 5 GHz bands

- IoT device package

- compact, planar geometry

- approximate size of a standard business card, 90 mm x 50 mm

- antennas integrated with electronics

- antennas placed along a long edge

- MIMO, two or three ports/ antennas for transmit and receive on each device

- maximized isolation between ports to create decoupled channels

This synthesis technology has also been expanded in the NI AWR Design Environment platform with the recent addition of the network synthesis module. Network synthesis creates optimized two-port impedance-matching networks composed of discrete and distributed components. Using evolutionary algorithms, the network synthesis wizard searches for the best circuit typologies and optimizes the component parameter values to improve component-to-component matching, power-amplifier design, amplifier inter-stage matching, and front-end system integration.

### Characterization and Production Goals

To fully understand a device's performance, characterization test engineers must validate its design during normal conditions, corner cases, and harsh

environments. Because of the exhaustive set of test requirements, characterization is typically performed on a small batch of devices. Conversely, production test engineers ensure the device is manufactured to the design specification at very high volumes while closely monitoring test throughput and yield. Although characterization test plans often call for testing under advanced conditions such as high temperature or with a dynamic power supply, production engineers may decide to avoid such conditions to reduce test time, especially if performance can be guaranteed by design.

These are just a few of the differences in the characterization and production test activities. however, there are many measurements performed in both activities. For example, adjacentchannel power ratio (ACPR) and error-vector magnitude (EVM) are often performed in both characterization and production. If a single piece of equipment can meet both the characterization and production requirements with a speed, quality, and price acceptable to both organizations, the handoff to production is smoother.

Maximizing commonality for both activities significantly reduces the time to market for a new product. Fortunately, the PXI platform is an open industry standard on which NI builds all of its test systems. Using this modular, open platform, both characterization and production engineers can benefit

from module-level upgrades to instrumentation and computer technology as test requirements evolve, further progressing product development as it moves closer to market.

#### Conclusion

The rapid evolution of wireless connectivity has driven continual consumer thirst for more data throughput and reduced time to market. The smaller form factor and integrated functionality offered by RF modules make them an attractive choice for designers looking for wireless connectivity from a drop-in component. For device manufacturers, modules represent an opportunity to become more competitive with devices that offer more capabilities, differentiation from competitors, and potentially larger cost margins.

To reap these benefits, companies will require multi-disciplinary engineering teams working together using a well-organized design flow that supports advanced design management, model libraries, integrated circuit, system, and EM co-simulation, and interoperability with CAD layout and multi-physics point tools. Fortunately, the design software and supporting test/ measurement solutions needed to support advanced module development are available and continue to evolve in step with the products they help bring to life. ◀