### Thales UK nutzt AWR-Software beim GaN-MMIC/Packaging-Design für das EU-MAGNUS Programm

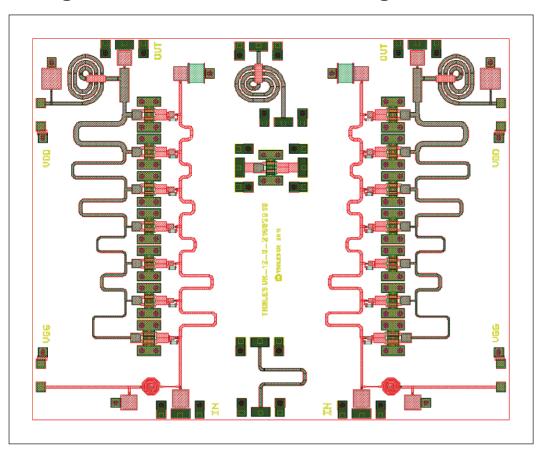

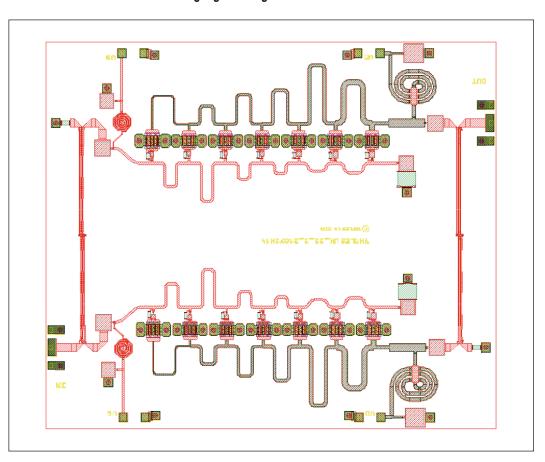

Bild 1: Layout des MMICs für den ersten Gießereibodenlauf. Verstärker wurden außerhalb des Chips kombiniert

Thales UK ist eines von sechs Unternehmen aus fünf europäischen Ländern, die in das MAG-NUS-Programm, ein europäisches Defense Agency Projekt einbezogen wurden. Das Ziel dieses Projektes ist es, europäische Anwendungstechnologien für Gallium-Nitrid (GaN) und Silicon (SiC) zu entwickeln. Die Technologien sollen in modernsten Radaranlagen, der

Kommunikation und in elektromagnetischen Systemen für die elektronische Kriegsführung eingesetzt werden, und zwar im elektromagnetischen Spektrum von 2-18 Gigahertz. Thales UK war für das Design von 10-W-GaN- MMICs verantwortlich, basierend auf dem

0.25-um-Foundry-Prozess von United Monolithic Semiconductors. Parallel zu dieser Aktivität wurden auch Arbeiten im Bereich der Verpackungsgestaltung und der thermischen Analyse durchgeführt. Sobald die MMICs realisiert und verpackt worden waren, wurden sie dazu verwendet, ein Demonstrationssystem aufzubauen, das Thales UK dann verwendete, um einen 30-W-MMIC-Leistungsblock zu designen. Dafür waren zwei Foundry-Läufe vorgesehen. Tabelle 1 zeigt die Spezifikationen des MMICs.

Die Ziele für dieses Design waren: Ein Frequenzbereich von 6 - 18 GHz, 10 dB Verstärkung und 10 W Ausgangsleistung. Es wurde entschieden eine nichtuniforme verteilte Topologie für den Verstärker zu verwenden, die ideal für Breitbandbetrieb geeignet ist, da sie in sich selbst stabil arbeitet. Das Ziel war, zwei verteilte Verstärker auf einem Chip zwischen einem Paar von Splittern/Combinern anzuordnen. Beim ersten Foundry-Lauf wurden die Verstärker außerhalb des Chips kombiniert, beim zweiten Foundry-Lauf erfolgte die Zusammenschaltung auf dem Chip.

#### Die Lösung

Die MMIC-Designs erfolgten unter Verwendung von Ni AWR Design Environment, spezi-

| AWR Group,    | NI |

|---------------|----|

| www.awrcorp.c | om |

| Parameter         | Requirements        | Comments      |

|-------------------|---------------------|---------------|

| Frequency         | 8-18 GHz            | Aim: 6-18 GHz |

| Gain              | ≥ 10 dB             |               |

| Output power      | ≥ 10 W              |               |

| Input return loss | ≥ 7 dB              | Aim: ≥ 10 dB  |

| Duty cycle        | 20%                 |               |

| PAE               | > 20%               |               |

| Drain bias        | 25-30 V             |               |

| Chip size         | 5x4 mm <sup>2</sup> |               |

Tabelle 1: Spezifikationen des MMIC

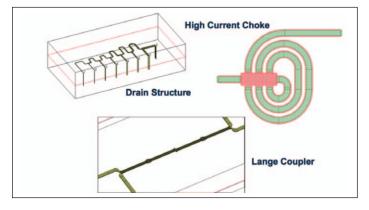

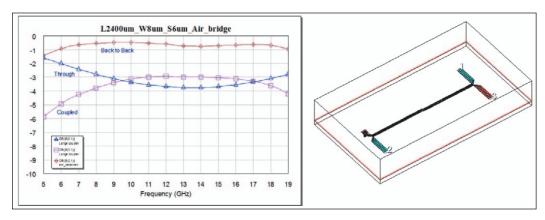

Bild 2: Passive Strukturen, simuliert in AXIEM

54 hf-praxis 9/2017

ell mit der Microwave Office Schaltungsdesign-Software. Die passiven Strukturen wurden im AXIEM 3D Planar EM-Simulator simuliert und das Package schließlich in Analyst, einem nach der Finite Elemente Methode arbeitenden EM-Simulator untersucht.

Das Layout des MMICs für den ersten Foundry-Lauf, bei dem die Verstärker erst außerhalb des Chips kombiniert wurden, zeigt Bild 1. Die Drain- und die Gateanschlüsse, mit den Kondensatoren in Serie zu jedem FET, sind zu erkennen. Es gibt auch einen Shunt-Widerstand, der die FETs mit der benötigten Vorspannung versorgt. Das Team musste allerdings eine eigene Hochleistungs-Induktivität entwickelt, was mit Hilfe von NI WAR Design Environment erfolgte.

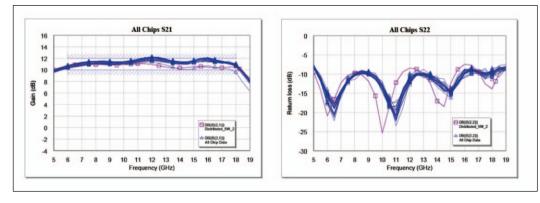

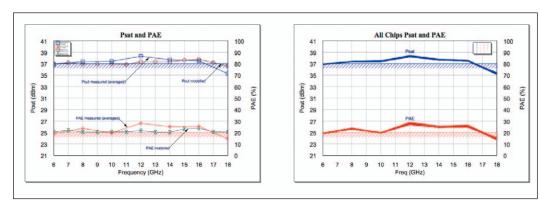

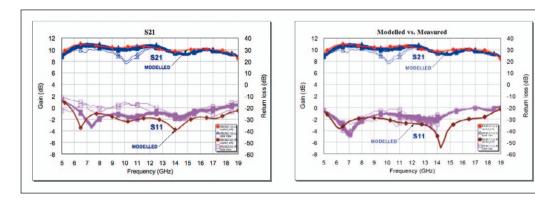

Bild 2 zeigt die passiven Strukturen (Hochstrom-Drossel, Drain-Struktur, Lange-Koppler), simuliert in AXIEM. Aus Bild 3 sind die Kleinsignal-Onwafer-Ergebnisse zu ersehen, die beim ersten Lauf für S21 und S22 erreicht wurden. Die magenta-farbene Linie entspricht der simulierten Verstärkung, die etwas größer als 10 dB ist. Es gab eine hervorragende Übereinstimmung zwischen den gemessenen und den simulierten Ergebnissen. Das galt auch für die Ausgangsleistung und die PAE, wie Bild 4 deutlich zeigt. Ungefähr 5 W Output lieferte jeder einzelne Verstärker, bei leichten Abfall am oberen Bereichsende 18 GHz. Der Wirkungsgrad lag im ganzen Band über 20 Prozent. Die Tabelle zeigt die Ergebnisse für alle Chips:.

# Der erste Foundry-Lauf erbrachte folgende Ergebnisse:

Durchschnittliche Verstärkung > 10.5 dB

Verstärkungsschwankungen über der Frequenz: ±0.75 dB

Schwankungen bei S21 < 1 dB

Bild 3: On-wafer-Ergebnisse, die beim ersten Foundry-Lauf für S21 und S22 erzielt wurden

Bild 4: Simulationsresultate für Ausgangsleistung und PAE

Bild 5: Layout des MMICs für den zweiten Foundry-Lauf

hf-praxis 9/2017 55

Bild 6: Simulierte Resultate für den Lange-Signalkoppler

Bild 7: On-chip-Resultate für Verstärkung und Rückflussdämpfung beim zweiten Foundry-Lauf

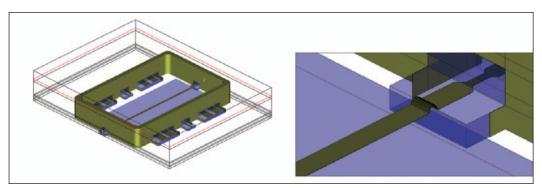

Bild 8: MMIC-Package des ersten Laufs, simuliert in Analyst. Dabei ist a) das komplette Package simuliert mit einer Microstrip-Leitung und b) ein Detail des keramischen Ports und des Bandübergangs

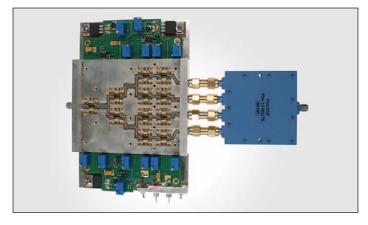

Bild 9: Verbindung der vier MMICs mit einem dämpfungsarmen Combiner

Rückflussdämpfung am Eingang > 12 dB

Rückflussdämpfung am Ausgang > 8.5 dB

Stabiler k-Faktor >1

Ausgangsleistung, unsymmetrisch ~37 dBm

Verbreitung < 0.5 dB

Flacher, gesättigter Ausgangsleistungsverlauf über der Frequenz, Welligkeit <0,5 dB

PAE ~ 20%

Elektrischer Ertrag: 100%

## Lange Signalkoppler - gute Wechselbeziehung

Den zweiten Foundry-Lauf zeigt Bild 5. Das Design-Kit wurde für diesen Lauf von v2 zu v3.1 geändert, was zu einer anderen Geometrie des FETs aus dem ersten Lauf führte. Bild 6 zeigt die simulierten Resultate des Lange Signalkopplers. Einige Daten: Länge = 2400 μm, Breite = 8  $\mu$ m, Separation = 6  $\mu$ m, Verlust = 0.3 dB pro Koppler. Bild 7 zeigt die On-wafer-Resultate des zweiten Foundry-Lauf. Auch dabei zeigte sich wieder eine ausgezeichnete Übereinstimmung von Verstärkung und Rückflussdämpfung. Bild 8 zeigt das MMIC-Package des ersten Laufs, simuliert in Analyst. A ist das komplette Package, B ein Detail des keramischen Ports und des Klebebandüberganges.

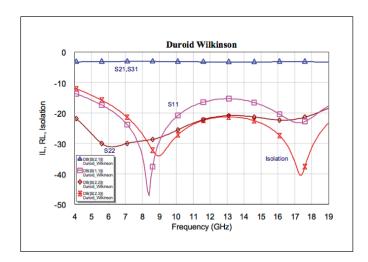

Der letzte Schritt des Programms bestand darin, ein Demonstrationssystem zu entwerfen, in dem die MMICs eine Aufgabe übernahmen. Das Designteam verwendete Microwave Office für den Entwurf eines 30-W-MPM mit einem dämpfungsarmen Leistungs-Combiner und einer Schaltung zur Bias-Einstellung und Kontrolle. Bild 9 zeigt die vier MMICs und ihre Verbindung mit dem dämpfungsarmen Combiner. Aus Bild 10 sind die Resultate des Wilkinson-Leistungsteilers zu ersehen, der in einer Ni AWR Design Umgebung entwickelt wurde.

56 hf-praxis 9/2017

Bild 10: Resultate des in Ni AWR Design Environment designten Wilkinson-Leistungsteilers

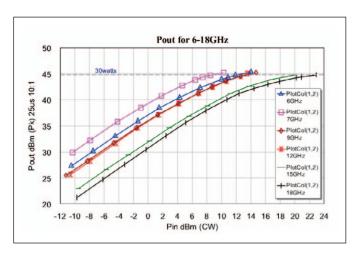

Bild 11: Gemessene Leistung im Bereich von 6-18 GHz

### **Hier einige Daten:**

- Eingangs-Rückflussdämpfung >15 dB

- S22 kleiner als -20 dB

- Entkopplung > 17 dB

- Verstärkung 33 40 dB

- Return Loss: 10 dB

- Ausgangsleistung: 30 W, gemessen zwischen 6 und 18 Gigahertz, wie Bild 11 zeigt.

### Warum Ni-AWR Design Environment

Entscheidend für den Erfolg dieses Projekts waren die extrem genauen Modelle der Ni-WAR-Design-Umgebung. Die Möglichkeit, beim Design nahtlos zwischen der Microwave Office Design-Umgebung, der AXIEM EM-Simulation der passiven Elemente und der Analyst EM-Simulation des Packages hin und her zu wechseln, erleichterte den schnellen Ablauf des Projekts beträchtlich. ◀

#### Über Thales UK

Thales UK ist einer der weltweit führenden Pioniere in den Bereichen Luft- und Raumfahrt, Verteidigung, Transportwesen, Sicherheit und Raumfahrttechnik. Das Unternehmen stellt weltweit führende Technologie für den zivilen und den Verteidigungsbereich her.

hf-praxis 9/2017 57