### HF-Technik hilft IT-Entwicklern:

## Schnelle Signale auf HF-Leitungen

HF-technische Grundlagen werden in der modernen Informationstechnik immer wichtiger. Hier erreichen die Bit-Raten, und mehr noch die Taktfrequenzen, etwa aus Quarzgeneratoren, immer höhere Werte. Der Beitrag zeigt dies beispielhaft anhand der Ausbreitungsverzögerung einer elektromagnetischen Welle auf einer belasteten HF-Leitung und deren Terminierung.

In der Informationselektronik ist nicht nur die Speicherfähigkeit beständig gestiegen, sondern auch die Bit-Raten wurden in die Höhe getrieben. Damit verbunden sind entsprechend hohe Taktfrequenzen. Naturgemäß stellen diese den frequenzmäßigen Flaschenhals dar.

## Immer schnellere digitale und Takt-Signale

Beide Entwicklungen sind den Fortschritten in der Halbleitertechnologie zu verdanken, die

immer kleinere Strukturen ermöglicht hat. Daher konnten

immer mehr Informationen

auf einer gegebenen Fläche

gespeichert werden, aber auch

die parasitären Größen mikroelektronischer aktiver Bauelemente schrumpften, sodass

höhere Transitfrequenzen möglich wurden.

Diese Bauelemente können auch sehr schnelle digitale Signale verarbeiten, denn Anstiegs-, Abfall- und Verzögerungszeiten sind indirekt proportional zur Grenzfrequenz eines Systems. Je schneller jedoch die digitalen Signale sind, umso kritischer

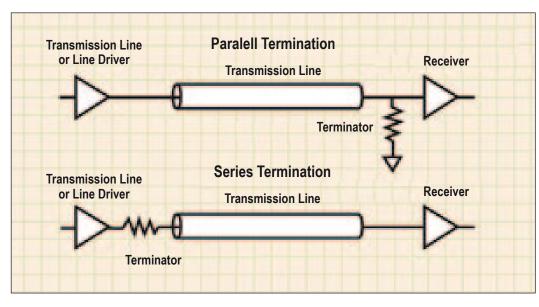

Bild 1: Parallelle und serielle Termination, wie sie typisch in der Digitaltechnik ist (Quelle: [2])

wird die Übertragung auf Leitungen. Im Zuge der technischen Entwicklung haben daher HF-Leitungen auch in der Digitalund Computertechnik immer mehr an Bedeutung gewonnen. Digitale Bausteine werden z.B. durch genau berechnete Microstrip-Leitungen verbunden.

Neben Faktoren wie dem Wellenwiderstand und der Dämpfung spielt dabei die Ausbreitungsverzögerung der elektromagnetischen Welle auf der belasteten Leitung, die Loaded Transmission Line Propagation Delay, eine oft zu beachtende, aber auch leicht zu übersehende Rolle. Ebenso verdient die Terminierung Beachtung, um störende Reflexionen zu vermeiden oder wenigstens gering zu halten.

## Die Ausbreitungsgeschwindigkeit

Im Vakuum breitet sich eine elektromagnetische Welle mit Lichtgeschwindigkeit aus, in Luft nahezu mit Lichtgeschwindigkeit. In Koaxialkabeln und bei Leitungen auf Platinen ist die Ausbreitungsgeschwindigkeit mehr oder wenig geringer, da sie vom Dielektrikum, also vom Isolationsmaterial

zwischen den beiden Leitern bestimmt wird. Man hat daher einen Verkürzungsfaktor (Velocity Factor) eingeführt, der bei realen Koaxialkabeln z.B. 0,66 beträgt. Die Ausbreitungsgeschwindigkeit beträgt hier also nicht 300.000 km/s (Vakuum), sondern nur 200.000 km/s. Dieser Verkürzungsfaktor passt sehr gut in die analoge HF-Technik, wo bei Leitungen oft nicht die reine mechanische Länge, sondern die sogenannte elektrische Länge von Bedeutung ist. Dies ist die relative Länge im Verhältnis zur Wellenlänge des Signals. Angenommen sei ein Signal mit 300 MHz, dann beträgt die Wel-

$$\frac{300.000.000 \text{ m/s}}{300.000.000 \text{ Hz}} = 1 m$$

Dies gilt nur im Vakuum! Nur eine HF-Leitung von 0,5 m Länge mit Luft-Dielektrikum (Velocity Factor 1) hätte also bei 300 MHz die elektrische Länge von rund einer halben Wellenlänge (λ). Eine HF-Leitung von 0,5 m Länge mit dem Verkürzungsfaktor 0,66 hätte hingegen eine elektrische Länge von 0,76 λ.

Eine Leitung mit diesem Dielektrikum, die nur eine halbe Wel-

lenlänge lang sein soll, müsste die mechanische Länge 0,5 m x 0,66 = 0,33 m aufweisen. Man sieht sehr gut, wie treffend der Begriff Verkürzungsfaktor ist.

Im Gegensatz zur analogen HF-Technik spielt bei der Übertragung digitaler Signale die elektrische Länge der Leitung so gut wie keine Rolle. Hier ist von Interesse, welche Verzögerung ein Signal über einen bestimmten Längenabschnitt oder über die ganze Länge der Leitung erfährt. Dies wird durch die Propagation Delay ausgedrückt, eine Verzögerungszeit (t<sub>nd</sub>). Auch diese wird vom Dielektrikum bestimmt, welches wiederum Einfluss auf die Längsinduktivität L und die Parallelkapazität C der Leitung pro Längeneinheit hat. Würde man diese Größen kennen, könnte man sie nach der Formel

$$t_{pd} = \sqrt{L \times C}$$

errechnen. Würde man alternativ die Dielektrizitätskonstante und den Wellenwiderstand kennen, könnte man eine etwas komplexere Formel bemühen. Beides erübrigt sich heutzutage, denn dies erledigen viele Leitungsberechnungsprogramme nebenbei mit. Ein Wert für eine Microstripline mit 117 Ohm als

58 hf-praxis 5/2017

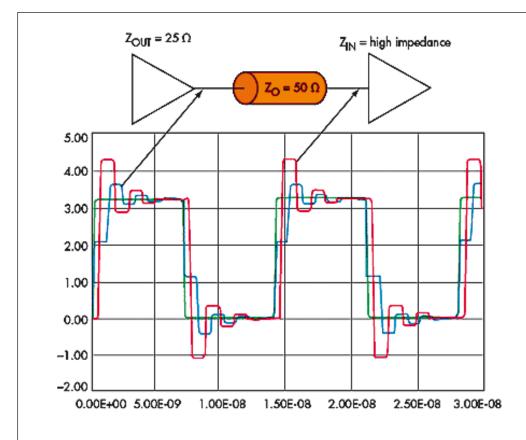

1. In this simulation, reflection is due to an unterminated transmission line. The green signal represents the ideal signal, and the blue and red signals are the driver's side and receiver's input, respectively.

Bild 2: Reflexionen verändern die Signalform an der Last (Quelle: [3])

Wellenwiderstand (Z<sub>0</sub>) und 4,7 als Dielektrizitätskonstante ist beispielsweise 1,73 ns/ft.

### Bedeutung der Propagation Delay

Die Ausbreitungsgeschwindigkeit ist in der Digitaltechnik immer dann von Bedeutung, wenn Baugruppen parallel betrieben oder synchron getaktet werden. Kommt es dann nämlich zu Laufzeitunterschieden zwischen den beteiligten Signalen und/oder dem Takt, so können Störsignale entstehen. Dieses Problem der Hazards (Signal-Wettläufe) oder Störspitzen (Spikes) ist dem Praktiker gut bekannt.

Und nun wird es noch ein wenig problematischer: Denn der von den Programmen ausgegebene Wert der Propagation Delay gilt nur für die unbelastete oder rein ohmsch abgeschlossene (terminierte) Leitung. Hat die Last eine Blindkomponente, wie dies in der Digitaltechnik typisch und unvermeidlich ist (Eingangskapazität der digitalen Baustufen), so genügt die nominelle Verzögerungszeit zur exakten Schaltungsdimensionierung nicht mehr.

# Propagation Delay und kapazitive Belastung

Die Verzögerungszeit nimmt bei kapazitiver Belastung zu. Gefragt ist also hier ebenfalls ein Faktor, der diese Zunahme beschreibt. Dieser errechet sich aus zwei Kapazitäten:

$$Zunahme = \sqrt{1 + \frac{C_L}{C_0}}$$

$C_L = Lastkapazität$

$C_0$  = Intrinsic Capacitance

Für die Intrinsic Capacitance der Leitung gilt:

$C_0$  in pF =  $t_{pd}$  in ns /  $Z_0$  in kOhm

Für die oben genannte Microstrip-Leitung würde bei 1 ft Länge gelten:

$$C_0$$

in pF = 1,73/0,117 = 1,5

Angenommen, diese Leitung muss fünf digitale Bausteine mit je 10 pF Eingangskapazität bedienen, die alle an ihrem Ende liegen, dann beträgt die Verzögerungszeit:

$$1,73 \text{ ns } x \sqrt{1 + \frac{50 pF}{15 pF}} = ,$$

$$= 1,73 \text{ ns } x 2,08 = 3,6 \text{ ns}$$

Dies bedeutet nicht, dass das Signal auf der Leitung langsamer vorankommt, es läuft immer mit der nominellen Geschwindigkeit von hier 1,73 ns/ft auf der Leitung. Jedoch kommt es erst nach 3,6 ns wegen der Ladung/Entladung der Kapazität am Ende zur Wirkung.

## Leitungswiderstand und kapazitive Belastung

In der analogen HF-Technik führt ein Fehlabschluss einer Leitung immer dazu, dass sich im eingeschwungenen Zustand Spannung und Strom an der Quelle so einstellen, dass sie nicht den Werten bei Leistungsanpassung entsprechen. Die Quelle erscheint gegenüber Leistungsanpassung weniger oder mehr belastet, sie gibt nicht die maximal mögliche Leistung ab. Dies wird in der Digitaltechnik auch nicht verlangt, denn bei der Informationsübertragung steht die Störsicherheit im Vordergrund. Fehlanpassungen sind hier deshalb störend, weil sie Reflexionen verursachen, welche den Störabstand herabsetzen oder die Funktion völlig lahmlegen können.

Bei Leistungsanpassung sieht die Quelle ihren eigenen Innenwiderstand. Bei Fehlanpassung sieht sie gewissermaßen einen davon abweichenden Widerstand, dem Spannung und Strom entsprechen. Bei kapazitiver Belastung wird diese Impedanz (Z) in der Applikationsschrift [1] ähnlich wie die neue Verzögerungszeit berechnet:

Nenn-Wellenwiderstand

$$\sqrt{1 + \frac{C_L}{C_0}}$$

Es wird keine ohmsche Belastung angenommen. Die Quelle würde demnach

$$117 \text{ Ohm}/2,08 = 56 \text{ Ohm}$$

sehen. Dass dies generell, also unabhängig von der Leitungslänge, der Fall sein soll, kommt möglicherweise dem in der Analogtechnik tätigen HF-Techniker fragwürdig vor.

### Hintergrund-Info dazu:

In der analogen HF-Technik bestimmen bei einem Fehlabschluss und somit Reflexionen die Leitungslänge (genauer die elektrische Länge), wie Gesamtspannung bzw. Gesamtstrom an der Quelle ausfallen und wie groß somit die Impedanz ist,

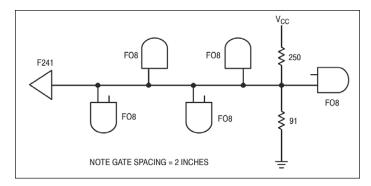

Bild 3: Fünf digitale Gatter, verteilt an einer HF-Leitung (Quelle: [1])

welche man direkt an die Quelle anschließen müsste, damit sich genau diese Verhältnisse ergeben. Über die Leitungslänge wird hier der Wirkungsgrad beeinflusst, während die Leistung in die Last gleich bleibt. (Vorausgesetzt, Quellwiderstand und Wellenwiderstand der Leitung sind gleich.) In die Last geht die Leistung X, aber die Quelle kann dabei bei der Leitungslänge Y eine hohe Impedanz sehen (guter Wirkungsgrad, über 50%) oder bei der Leitungslänge Z eine niedrige Impedanz (schlechter Wirkungsgrad, unter 50%). Dies lässt sich anhand konkreter Berechnungen oder im praktischen Experiment sehr leicht zeigen bzw. beweisen.

#### Zur Störfestigkeit

In der IT mit ihren schnellen digitalen Signalen interessiert die Aufrechterhaltung der theoretisch möglichen Störfestigkeit. Ist die Last größer als der Wellenwiderstand der Leitung, addieren sich ankommende und reflektierte Spannung, und die Störfestigkeit sollte nicht leiden. Ist die Last jedoch kleiner als der Wellenwiderstand, so erleidet die reflektierte Spannung bei der Reflexion einen sogenannten Phasensprung, wird also umgepolt. Ein H-Signal tritt nun im Pegel vermindert am Eingang der digitalen Baugruppe auf, ein klarer Fall von weniger Störfestigkeit.

Erfolgt eine Reflexion an der Last und stimmen Quell- und Wellenwiderstand nicht überein, so wird das rücklaufende Signal an der Quelle wiederum teilweise reflektiert. Dieser Anteil und das aktuelle Signal direkt aus der Quelle laufen parallel über die Leitung zur Last, wo nun beide Signale teilweise reflektiert werden. Da die Leitungslänge darüber entscheidet. wann ein an der Last reflektierter Signalanteil an der Ouelle auftaucht, lässt sich darüber auch beeinflussen, ob ein H mit einem H zusammenfällt oder ein L mit einem H. Daher entscheidet nun auch die Leitungslänge über die Störfestigkeit. Bild 1 illustriert einen eher harmlosen Fall, bei dem sowohl im H- als auch L-Bereich am Eingang der digitalen Baustufe die Extremabweichungen in ungefährlichen Grenzen bleiben. Das Signal an der Quelle ist irrelevant, da es nicht weiterverarbeitet wird.

## Optimaler Leitungsabschluss

Zur Vermeidung insbesondere der letzten Situation, die schwer durchschaubar ist, sollte man bei unangepasster Last dafür sorgen, dass an der Ouelle keine nennenswerte Rückreflexion erfolgen kann. Dies führt zum Thema der Termination einer Leitung. Außerdem wäre keine Diskussion über HF-Leitungen komplett ohne die Darstellung der Techniken für den optimalen Abschluss der Leitung (Termination). Dieser Punkt ist in der Informationstechnik von besonderer Bedeutung, da er die Reduzierung von Reflexionen, also die Optimierung der Störfestigkeit direkt betrifft.

Grundsätzlich sind drei Fälle/ Methoden zu unterscheiden:

• nicht terminierte (unterminated) Leitung

- parallele Termination

- serielle Termination

## Die nicht terminierte Leitung

In der analogen HF-Technik entscheidet letztendlich die Phasenbeziehung zwischen Nutzsignal und reflektiertem Signal an der Quelle über die gesamte Spannung (den gesamten Strom) dort. Verlängert man eine Leitung um genau eine Wellenlänge, so ändert sich nichts, da dies 360° Phasendrehung bedeutet, was auch mit 0° interpretiert werden kann. Je länger die Leitung bis zu einer Wellenlänge ist, umso größer die Phasendrehung. Je kürzer die Leitung, umso drastischer sind die Auswirkungen einer Fehlanpassung. Daher bezeichnet man Leitungen, die kürzer sind als ein Zehntel der Wellenlänge als elektrisch kurz und vernachlässigt sie. Die Schaltung wird so betrachtet, als ob die Leitung nicht vorhanden wäre.

Bei den schnellen digitalen Signalen entscheidet ebenfalls die Leitungslänge über den Grad der Störung zwischen reflektiertem Signal und Nutzsignal. Auch hier kann man davon ausgehen, dass es nur zu vernachlässigbaren Störungen infolge Reflexionen kommt, wenn die Leitung elektrisch kurz ist. Dies muss natürlich bei der höchsten vorkommenden Bit-Rate der Fall sein. Eine einfache Terminierung mit einem Widerstand ist dann meist nur von Nachteil, da jeder zusätzliche Widerstand eine Signalreduzierung am zu beliefernden Eingang verursacht

Wichtig ist, dass die Propagation Delay unter Last (Loaded Delay) klein ist gegenüber der Anstiegs- und Abfallszeit des Signals. Die entsprechenden Spezifikationen der verwendeten Logik-Familie sind zu prüfen. Daumenregel: Die Laufzeit der belasteten Leitung darf nicht größer sein als ein Viertel der kürzesten dieser Zeiten (Anstiegs- und Abfallszeit unterscheiden sich in der Regel wenig). Ist beispielsweise die

Anstiegszeit mit 6 ns die kürzere, darf die Loaded Delay nicht über 1,5 ns liegen.

### **Parallele Termination**

In diesem Fall legt man einen Widerstand parallel zum Außenwiderstand, falls dieser größer als der Wellenwiderstand ist. Im IT-Bereich ist dies in der Regel der Eingangswiderstand (die Last). Im Bild 2 oben sieht man diese Termination. Der sich ergebende Gesamtwiderstand sollte etwas größer sein als der Wellenwiderstand, da ja noch die Eingangskapazität mit parallel liegt. In [1] wird angemerkt, dass diese Methode der Terminierung einen erhöhten Signalstrom erfordert und dass ein entsprechender Treiber auszuwählen ist. Das scheint jedoch nur auf den ersten Blick so, da die Quelle sowieso zunächst einen Strom entsprechend des Wellenwiderstands aufbringt. Dieser belastet ja die Quelle wie ein ohmscher Widerstand. Die Spannung, die sich zunächst am Eingang einstellt, tritt dann auch an der terminierten Last auf. Es lohnt sich dennoch, zu prüfen, ob die Terminierung überhaupt erforderlich ist. Das ist nicht der Fall, wenn Quelle und Leitung angepasst sind. Das Signal an der Last erhöht sich dann immer, und der reflektierte Anteil verschwindet in der Quelle, ohne infolge erneuter Reflexion zu stören.

### **Serielle Termination**

Die serielle Termination wird im IT-Bereich in der Regel an der Quelle praktiziert (Bild 2). Sie verhindert die kritische Rückreflexion. Die HF-Leitung mit einem eventuell zur Quelle zurückkehrenden Signalanteil sieht ihren Wellenwiderstand, daher ist hier keine Reflexion. Ist der Lastwiderstand kleiner als der Wellenwiderstand, was bei mehreren parallel liegenden Verbrauchern der Fall sein kann, wendet man die serielle Termination an. Beispiel: Es liegen fünf Gatter mit je 400 Ohm Eingangswiderstand parallel am Ausgang einer 117-Ohm-Stripline. Der gesamte Lastwiderstand ist 80 Ohm, ein 33-Ohm-Wider-

60 hf-praxis 5/2017

stand wird in Serie geschaltet, sodass die Stripline 113 Ohm sieht.

#### Parallel oder seriell?

Oft wird eine der Terminations-Methoden genügen. Aber welche sollte es dann sein? Die Antwort ist einfach: Man bildet das Verhältnis von Außenwiderstand zu Wellenwiderstand und terminiert dort, wo es am kleinsten ist. Dann nämlich erfolgt auch der kleinste Signalverlust. Hat man einen leistungsfähigen modernen Treiber, wird dies meist die Lastseite sein. Sind mehrere Lasten über die Leitung verteilt angeschlossen, dann ist die serielle Termination an der Quelle aber kritisch. Dann sollte an der Last terminiert werden.

### FS

#### Quellen:

- [1] Reflections on Transmission Line Effects, Motorola Application Note AN1061

- [2] www.electronicproducts. com/Passive\_Components/ Resistors\_and\_Potentiometers/ Terminating\_transmission\_ lines.aspx

- [3] http://electronics.stackex-change.com/questions/33125/short-distance-board-to-board-communication

- [4] http://williamson-labs.com/xmission.htm

- [5] www.compliance-club.com/ archive/old\_archive/991005.htm

Empfehlenswerte Bücher:

Terry Edwards, Michael Steer: Foundations for Microstrip Circuit Design, 4th Edition, April 2016, ISBN 978-1-118-93619-1

Frank Sichla: HF-Leitungen verstehen und nutzen, DARC-Verlag Baunatal 2012, ISBN 978-3-88692-061-7

Clayton R. Paul: Transmission Lines in Digital and Analog Electronic Systems: Signal Integrity and Crosstalk, Oktober 2010, ISBN 978-0-470-59230-4

W. Sinnema: Electronic Transmission Technology, Prentice-Hall, Englewood Cliffs, New Jersey, 1979

## Ein praktisches Beispiel

Angenommen sei ein Leitungssystem nach Bild 3 mit folgenden Eigenschaften:

- V<sub>CC</sub> 5 V

- Z<sub>0</sub> der Leitung 117 Ohm

- Unloaded Propagation Delay 1,73 ns/ft

- Logikfamilie: Fast TTL bei Treiber und Gattern

- Treiber: F241,  $t_r = t_f = 2$  ns (für 50 pF Bürdekapazität)

- Anzahl der Lasten (Typ F08): 5

- Eingangskapazität jeder Last: 5 pF

- Eingangsströme jeder Last:  $I_{IL} = -600 \mu A$ ,  $I_{IH} = 100 \mu A$

- Konfiguration: örtlich verteilte Lasten, etwa aller 2 inch

- Leitungslänge 10 inch

### 1. Berechnung der Intrinsic Capacitance

$$C_0 in pF = \frac{t_{pd} in ns}{Z_0 in k\Omega}$$

$C_0$  in pF = 1,73 ns / 0,117 = 15 pF/ft = 1,25 pF/inch = 12,5 pF/10 inch

2. Berechnung der Loaded Propagation Delay

$$t_{pd} = \sqrt{1 + \frac{C_L}{C_0}}$$

$t_{pd} = 1,73 \text{ ns/ft} = 0,144 \text{ ns/inch} = 1,44 \text{ ns/10 inch}$

Das ist viel mehr als 1/4 der Anstiegs- bzw. Abfallzeit (je 2 ns). Daher muss terminiert werden.

3. Berechnung der Loaded Line Impedance

$$Z = \frac{Z_0}{\sqrt{1 + \frac{C_1}{C_0}}} \qquad Z = \frac{117 \,\Omega}{\sqrt{1 + \frac{5 \, x \, 5 \, pF}{12, 5 \, pF}}} = 68 \,\Omega$$

Hier sind die Lasten über die Leitung verteilt, serielle Termination verbietet sich. Die parallele Terminierung erfolgt mit zwei Widerständen am Ende der Leitung. Der Treiber F241 erlaubt kräftige Ausgangsströme von  $I_{OL}$ = -64 mA und  $I_{OH}$ = 15 mA, daher ergeben sich entsprechende DC-Ausgangswiderstände. In etwa berechnen kann man sie so:

DC-Ausgangswiderstände =

$$\frac{V_{OH \text{ min}}}{\left(\left(5 \times 100 \ \mu A\right) + \frac{I_{OH}}{2}\right)} = \frac{2 V}{8 \ mA} = 250 \ \Omega$$

I<sub>OH</sub>/2 wurde willkürlich gewählt; der Wert kann, falls erforderlich, reduziert werden. Der Sink-Strom-Widerstand beträgt 91 Ohm. Dies ergibt sich aus einem Sink-Strom vom Treiber von:

Sink-Strom vom Treiber = Anzahl der Lasten x

$$I_{IH} + V_{CC} - \frac{V_{OL}(F241)}{91 \Omega}$$

Man erhält 5 x 600  $\mu$ A + 5 V - 0,55 V / 91 Ohm = 52 mA. Diesen Strom kann der Treiber aufnehmen. Der Parallelwiderstand der beiden Terminating-Widerstände sollte etwa dem Wellenwiderstand entsprechen, daher die 250 Ohm für den zweiten Widerstand. Die Leitung ist nun optimal abgeschlossen, und Reflexionen wurden minimiert.

In diesem Beispiel wurde die Kapazität in der Eingangsimpedanz der Lasten nicht mit sehr kurzen Leitungen (Stubs, Stummel) kompensiert. Solche Stubs sind immer elektrisch kurz, man nutzt nur ihre Induktivität aus. Dazu werden sie am Ende kurzgeschlossen und parallel zu den Eingängen gelegt. Für diese Stubs wäre eine extra Berechnung erforderlich, die in [1] vorgenommen wurde.

hf-praxis 5/2017 61