# Optimierung der Leistung elektronischer Schaltungsentwürfe durch Integration von Tests

Einführung: Herausforderungen beim Schaltungsentwurf

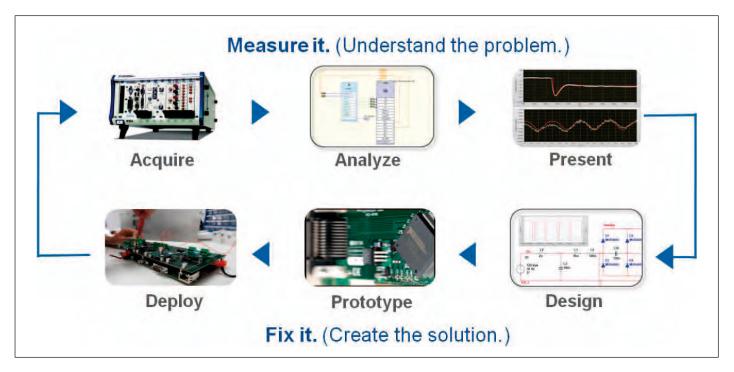

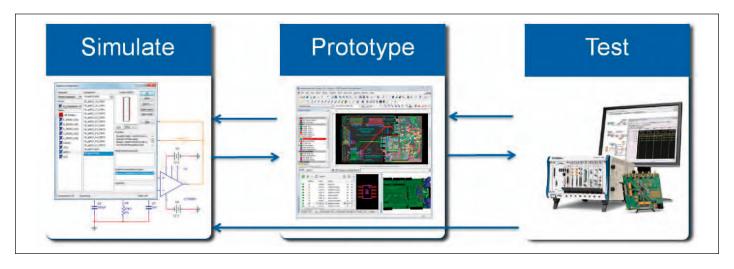

Bild 1: Stationen der Entwicklung eines Prototyps vor der Fertigung

In den letzten 50 Jahren sorgte das Moore'sche Gesetz für beachtliche Verbesserungen bei Leistung, Größe und Kosten von Halbleiterkomponenten. Des Weiteren schrieb das Gesetz R&D-Teams strengere Anforderungen vor, um kürzere Entwicklungszyklen zu erzielen. Da die Nachfrage nach Elektronikanwendungen in vielen Industrien und Gewerbebereichen steigt, arbeiten Designingenieure gelegentlich gleichzeitig an Schaltkreisen für zwei vollkommen unterschiedliche Applikationen, beispielsweise an Präzisionsverstärkern für Messtechnik in einem Avioniksystem und an einem Schaltnetzteil (SMPS) für ein Verbraucherprodukt.

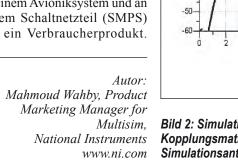

Bild 2: Simulationsergebnisse eines Ultrabreitband-Filters von 3,1 GHz bis 9 GHz; (a) Kopplungsmatrix zum Filtern, (b) ideale Antwort konzentrierter Elemente, (c) ursprüngliche 2D-EM-Simulationsantwort, (d) 3D-EM-Simulationsantwort nach Optimierung

10 hf-praxis 11/2014

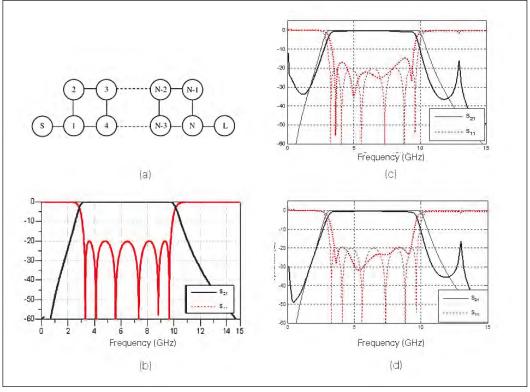

Bild 3: Prototyp eines GPS-Transceivers mit 1,6 GHz: Die Abbildung zeigt die Leiterplatte, die in NI Ultiboard – dem Werkzeug für Leiterplattenlayouts – entwickelt wurde, einen spannungsgesteuerten Oszillator in Microwave Office sowie Amplitudenreserven eines ZF-Verstärkers in Multisim.

Jedoch bleiben Entwurfsmethodik, Softwarewerkzeuge und die Testhardware am Prüfplatz, die Entwickler einsetzen, unabhängig vom Projekt gleich. Sieht man sich den Entwicklungsprozess von Schaltungsentwürfen genauer an, beginnt dieser immer mit dem Festlegen der Spezifikationen, die der finale Entwurf erfüllen muss. Basierend auf diesen Spezifikationen durchläuft der Entwurf mehrere Zyklen der Prototypenentwicklung, die den Einsatz von EDA-Werkzeugen (Electronic Design Automation, Entwurfsautomatisierung elektronischer Systeme) für Simulation, Layout, Systemintegration und Tests umfassen, bevor der fertige Entwurf an die Produktion weitergegeben wird. Die Kosten eines einzelnen Zyklus schwanken stark und hängen von der Art des Entwurfs und der Anwendung ab. Beispielsweise kann die Iteration eines Prototyps für einen digitalen Controller mit 40 MHz auf einer Leiterplatte mit sechs Schichten nur ein paar Tausend Dollar kosten und zwei Wochen Entwicklungszeit beanspruchen. Den Prototyp für das Frontend eines Mikrowellentransceivers auf einem Silizium-Germanium-Wafer zu entwickeln, kann hingegen Kosten von bis zu einer Viertel Million Dollar verursachen und Monate dauern. Bei Kosten in dieser Höhe ist es wichtig, sich EDA-Werkzeuge zu Nutze zu machen, um unnötige Ausgaben zu vermeiden und die Markteinführung neuer Entwürfe zu beschleunigen.

Die Auswahl der richtigen EDA-Werkzeuge stellt eine der wichtigsten Aufgaben von R&D-Managern dar. Zudem werden Techniken eingesetzt, die eine frühzeitige Testintegration in die Designphase ermöglichen, um die Leistung von Schaltungsentwürfen zu optimieren und Prototypenzyklen zu reduzieren. Während die Systementwicklung, einschließlich Designund Prüfverfahren, durch das "V-Modell" für mehrere Industrien, z. B. den Automobilsektor, ausreichend definiert wurde, machen sich Entwickler aus der Halbleiterindustrie die Integration von Tests noch nicht voll zunutze. Die nachfolgend vorgestellten Methoden zur Schaltungssimulation und die Integration von Testsequenzen verbessern entscheidend die Leistung von Schaltungsentwürfen.

## Vorteile mehrerer Simulationsansätze nutzen

Einer der schwierigsten Prozesse für Entwickler von Schaltkreisen bei der Arbeit mit EDA-Werkzeugen ist der Transfer eines Entwurfs von einem Werkzeug zu einem anderen. Für gewöhnlich ist dieser Prozess sehr fehleranfällig, führt zu einem komplizierten Bibliothekenmanagement, und ein Großteil der Entwurfsdaten geht verloren, auch dann, wenn die Werkzeuge Standard-Dateiformate akzeptieren. Ein weiteres Problem beim Hin- und Herwechseln zwischen mehreren EDA-Werkzeugen ist die Zeit, die benötigt wird, um den Umgang mit jedem Werkzeug zu erlernen. Trotz dieser Herausforderungen könnte der Einsatz mehrerer Werkzeuge den Designprozess produktiver gestalten, wenn sie richtig eingesetzt werden.

Als Anschauungsbeispiel dient die Entwicklung eines passiven Ultrabreitband-Mikrowellen-

12 hf-praxis 11/2014

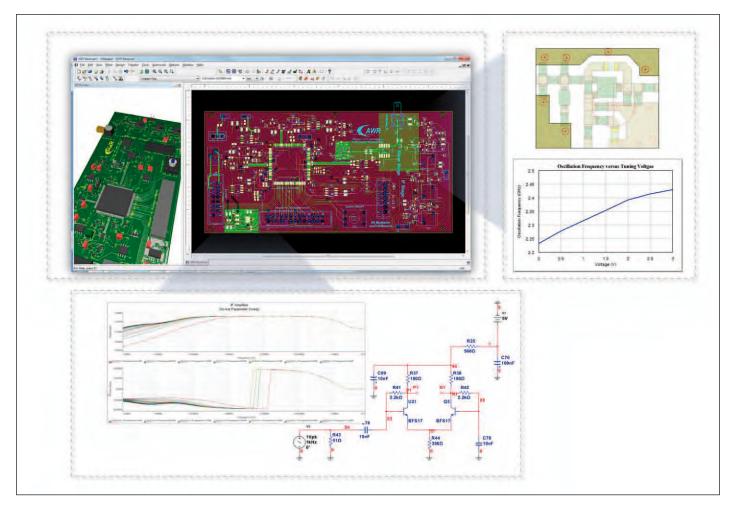

Bild 4: Integration von Tests in den Entwurfsprozess zur Beschleunigung der Markteinführung

filters. So kann etwa der Designer bei der Entwicklung der Kopplungsmatrix von Filtern ein mathematisches Synthesewerkzeug sowie eine Harmonic-Balance-Schaltungssimulation zur Evaluierung der von konzentrierten Komponenten modellierten Topologie nutzen. Anschließend verwendet er einen Simulator für zweidimensionale elektromagnetische Felder, um die erste Reaktion der physikalischen Implementierung auf der Platine zu berechnen, und zum Schluss eine vollständige 3D-EM-Simulation zur Entwurfsoptimierung. Obwohl dieses Ultrabreitband-Filter im 3D-EM-Simulator präzise entworfen werden könnte, würde es ohne Synthese, Schaltungssimulation und 2D-Simulatoren viel länger dauern. In diesem Fall ist der Einsatz mehrerer Werkzeuge gerechtfertigt. Zusammenfassend sind die größten Vorteile für EDA-Anwender kürzere Simulationszeiten eine erweiterte Komponentenbibliothek (und PDKs im Falle von Chipentwicklungen) sowie eine benutzerfreundliche Oberfläche.

Dieses Konzept ist für Systementwürfe, die analoge Hochfrequenz-Frontends, niederfrequente Schaltungen und Netzgeräte sowie digitale Controller umfassen, von noch größerer Bedeutung, da die Entwurfsaufgaben umfangreicher sind und erhebliches Fachwissen erfordern. Um die Möglichkeiten der

Modellierung und Simulation am Desktop voll auszuschöpfen müssen Designer den Einsatz mehrerer Entwicklungswerkzeuge zum Optimieren der Entwurfsleistung in Betracht ziehen. Bei diesem Entwurf eines GPS-Transceivers werden die Komponenten des Hochfrequenz-Frontends (Antenne, rauscharmer Verstärker und Mischer) in der HF-Entwicklungssoftware Microwave Office (MWO) von AWR entwickelt. Niederfrequente SPICE-Simulation (in einem Werkzeug wie beispielsweise NI Multisim) wird ebenfalls eingesetzt, um die Leistung der ZF-Verstärker und Netzgeräte zu evaluieren.

Zuletzt wird die Anordnung der stark verteilten Komponenten mithilfe des Hochfrequenzwerkzeugs entwickelt und anschließend an ein etabliertes Werkzeug für das Leiterplattenlayout übertragen, um den finalen Prototyp einer Leiterplatte zu erstellen. Durch diesen Wechsel können Entwickler ein hohes Maß an Genauigkeit beibehalten, indem der EM-Simulator für kritische Komponenten genutzt und die Zeit für Simulation und Prototypenerstellung reduziert wird. Letzteres gelingt durch die SPICE-Simulation, die für das restliche System zum Einsatz kommt.

#### Frühe Testintegration

Während der Übertragung der elektronischen Schaltungsentwürfe von EDA-Werkzeugen auf die Hardwareprototypen, wird die Charakterisierung des Prüflings (DUT) normalerweise nicht berücksichtigt. Wird jedoch eine Testplattform verwendet, die modular mit einer softwaredefinierten Architektur aufgebaut ist, wird die Integration in reale Messungen deutlich einfacher.

Diese Signale früh in den Entwicklungsprozess zu integrieren hat mehrere Vorteile. Eine Test Executive, die im Hintergrund das EDA-Werkzeug aufruft, ermöglicht den sofortigen Vergleich von Simulationsergebnissen, der gemessenen Frequenz und dem Einschwingverhalten des Schaltkreises. Aufgrund dieser Korrelation können Entwickler ihre Simulationsmodelle besser optimieren und neue Modelle erstellen, die auf realistischen Messungen des Streuparameters ihres Prüflings basieren.

Diese werden dann in zukünftigen Entwürfen eingesetzt. Simulationsmodelle, die auf Streuparameter-Frequenz-Tabellen basieren, lassen sich leicht erstellen und in gängigen SPICE-Simulationsumgebungen wiederverwenden.

Ein weiterer Vorteil des softwaredefinierten Testansatzes wird bei der Entwicklung von Optimierungsalgorithmen deutlich, die in der endgültigen Systemimplementierung ausgeführt werden. Hervorragende Beispiele für diesen Anwendungsfall stellen die HüllkurvenVerfolgung (Envelope Tracking, ET) und die digitale Vorverzerrung (DPD) dar – zwei Techniken, die in Anwendungen mit modernen RF-Leistungsverstärkern eingesetzt werden.

Dank des softwaredefinierten Ansatzes lassen sich diese Algorithmen einfach entwickeln und auf den Prüfling eines Verstärkers anwenden, wo die Messgeräte als Teil des Funksystems agieren. Hier liegt der Vorteil in der Validierung der Logik dieser Algorithmen zu einem frühen Zeitpunkt in der Entwicklungsphase und in der Optimierung des Verstärkerentwurfs durch eine frühe Integration in die Testhardware.

Entwickler von Schaltkreisen stehen mehreren Herausforderungen gegenüber, wenn strenge Designvorgaben mit Markteinführungszeiten in Einklang gebracht werden müssen. In diesem Entwicklungsprozess vertrauen sie in großem Maße auf EDA-Werkzeuge.

Die Wahl der Werkzeuge hat großen Einfluss auf die Entwicklungskosten und die Anzahl der Prototypenzyklen, die vor der Fertigung durchlaufen werden müssen. Erstklassige Werkzeuge ermöglichen eine einfache Integration in unterschiedliche Entwicklungskomponenten, die bei Gleichstrom- bis hin zu Mikrowellenfrequenzen arbeiten und sich nahtlos in Testhardware integrieren lassen.

14 hf-praxis 11/2014

### Multikanal-BER-Messungen bei 1 Tbit/s

Anritsu hat eine 32-Kanal-Synchronisierungsfunktion für mit 32 Gbit/s übertragene Datensignale in Form eines Upgrades ihres Signalqualitätsanalysators MP1800A vorgestellt. Die neue Funktion ermöglicht die Konfiguration von Messsystemen mit hoher Genauigkeit zur Durchführung von Messungen an ultraschnellen Next-Generation-Kommunikationstechnologien, die Datenübertragungsraten von 400 Gbit/s und 1 Tbit/s nutzen.

Bis zu vier Mainframe-Einheiten MP1800A lassen sich mit der Upgrade-Option jeweils pro Mainframe mit einem Achtkanal-32-Gbit/s-Pulsmustergenerator synchronisieren. Die Mainframe-Einheiten können anschließend zum Messen der Funktion der neuen Kommunikationstechnologien, wie z.B.

Quad-DP-16QAM und Dual-DP-64QAM, eingesetzt werden. Diese Technologien nutzen Phasenmodulationsverfahren als Mittel zur Erweiterung der Kapazität von Kernnetzen bei Begrenzung der Bitrate pro Kanal. Durch die Installation von entweder vier Zweikanaloder zwei Vierkanal-32-Gbit/sPPG-Boards in vier miteinander gekoppelten MP1800A-Mainframes erhält man 32 Kanäle von 32 Gbit/s, wodurch eine Übertragungskapazität von 1 Tbit/s zur Verfügung steht. Mit einer hochpräzisen Funktion zum Einstellen der Phase in 2-mUI-Schritten (mUI = Milli-Einheitsschrittlänge) er-

möglicht der in den MP1800A verbaute 32-Gbit/s-PPG das einfache Konfigurieren eines Messsystems, das eine präzise Phasensteuerung bietet. Außerdem kann eine hohe Reproduzierbarkeit erreicht werden, da das 32-Gbit/s-Datensignal-Bitmuster des PPG als solches in jedem beliebigen Zeitintervall generiert werden kann.

Durch die Einbindung des neuen mit 32 Kanälen ausgestatteten 32-Gbit/s-PPG-Synchronisierungs-Upgrades in seine MP1800A-Messlösung kommen Forscher, Endgerätehersteller und Netzbetreiber bei der Realisierung der ultraschnellen Next-Generation-Netzwerktechnologien schneller voran.

■ Anritsu Corporation www.anritsu.com

## NETZWERKANALYSATOREN.

REFLEXION UND TRANSMISSION ELEKTRISCHER MESSOBJEKTE – AB 5 Hz BIS 67 GHz (BIS ZU 1,05 THz MIT OPTIONALEN FREQUENZ-EXTENDERN).

Ihr Spezialist für Mess- und Prüfgeräte

**VE!** sehen und testen.

inside tomorrow Halle A1 Stand 207